TSMC reveló nuevos detalles respecto a su próximo proceso de fabricación más avanzado, los 3nm, que ya tiene todas sus obleas reservadas hasta 2024 por Apple, AMD, NVIDIA, Intel, Qualcomm y Xilinx.

La empresa afirma que su nodo de 3nm permite ofrecer un aumento de velocidad del 10% al 15% consumiendo la misma energía que su proceso de fabricación de 5nm. Sin embargo, si lo que se busca es mejorar la autonomía manteniendo el mismo rendimiento, el silicio basado en los 3nm consumirá entre un 25% y 30% menos, mientras aumenta la densidad lógica en un 70%, la densidad de la SDRAM en un 20% y la densidad analógica en un 10%.

Además, un representante de la compañía taiwanesa, el Dr. Yuh Jier Mii, declaró que el proceso de fabricación de 3nm duplicó el número de «tape-outs» durante su primer año respecto a los 5nm. Este término hace referencia a los diseñadores de chips que finalizan sus diseños antes de enviarlos a la fábrica, que se encarga de perfeccionarlos o de pasar a la producción.

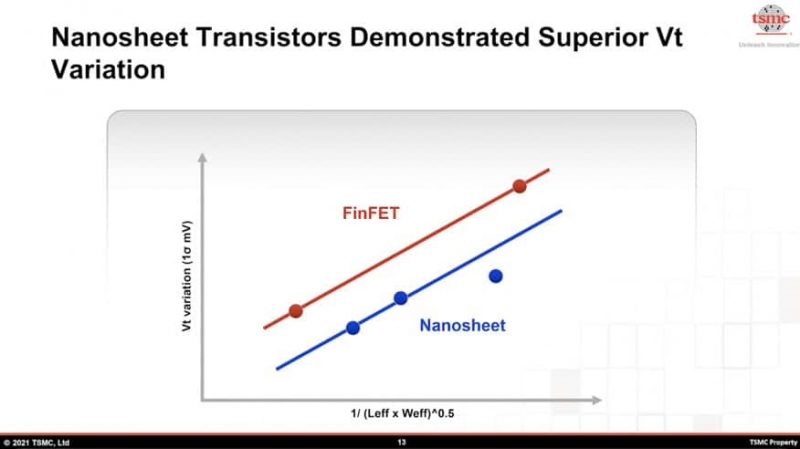

Por otro lado, el Dr. Mii compartió detalles clave de los circuitos que podrían acabar representando el salto de fabricación más importante de su empresa en años. Destacó que los transistores a nanoescala consiguieron aplicar un control más estricto del voltaje umbral (Vt). En el diseño de semiconductores, Vt se refiere al voltaje mínimo necesario para que un circuito funcione, y hasta las más mínimas variaciones pueden introducir limitaciones de diseño y caídas de rendimiento.

Según el directivo, los transistores de nano escala consiguieron «demostrar que los transistores de nano escala tienen variaciones de Vt un 15% menores, como se muestra en azul, en comparación con la de un transistor FinFET, como se muestra en rojo».

El futuro de TSMC con su nodo de 3nm se ve prometedor ¿Prefieren una mejora de rendimiento o de consumo?

Fuente: Wccftech