El becario senior de tecnología en TechInsights, Yuzo Fukuzaki, nos da un poco de información sobre la nueva tecnología de CPU que AMD presentó en su discurso principal de Computex 2021, 3D Vertical Cache (3D V-Cache). Luego, de que la compañía lo había detallado como una caché de último nivel de 64 MB adicional apilado sobre un CCD (matriz compleja del núcleo de la CPU), lo que mejora significativamente el rendimiento, incluida una ganancia promedio del 15% en el rendimiento de los juegos, lo que representa un rendimiento generacional increíble, sobre «Zen 3».

El prototipo que AMD presentó en su discurso de apertura se basó en un procesador con Socket AM4 con CCD «Zen 3» que tienen los componentes 3DV Cache en su lugar. Con dos de estos CCD, un procesador de 16 núcleos terminaría con 192 MB de caché L3.

La teoría de Yuzo Fukuzaki habla sobre la posición más plausible de 3D V-Cache en la jerarquía de la caché del procesador. Al parecer, amplía la caché L3 del CCD, y no sirve como caché «L4». De este modo, la configuración de la caché sigue siendo transparente para el sistema operativo, que la ve como un bloque contiguo de 96 MB de caché L3 (por CCD).

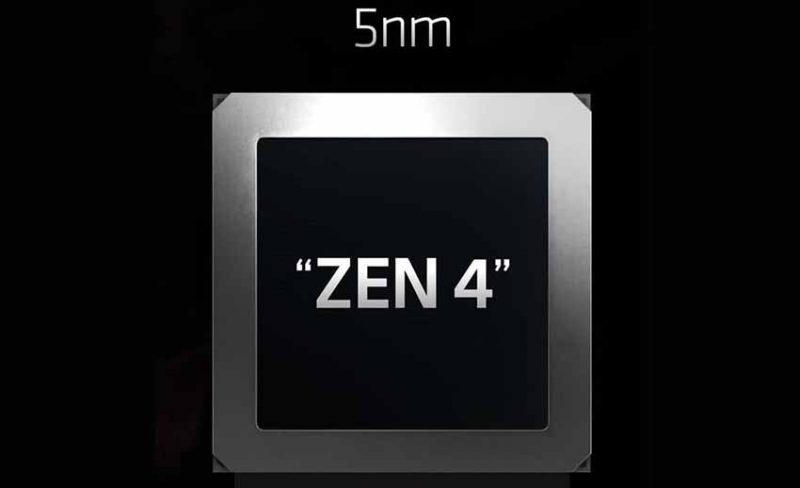

La matriz 3DV Cache es un chip SRAM fabricado con el mismo proceso de 7 nm que el CCD «Zen 3». Mide 6 mm x 6 mm (36 mm²) y se encuentra por encima de la región del CCD que normalmente tiene la SRAM L3 de 32 MB.

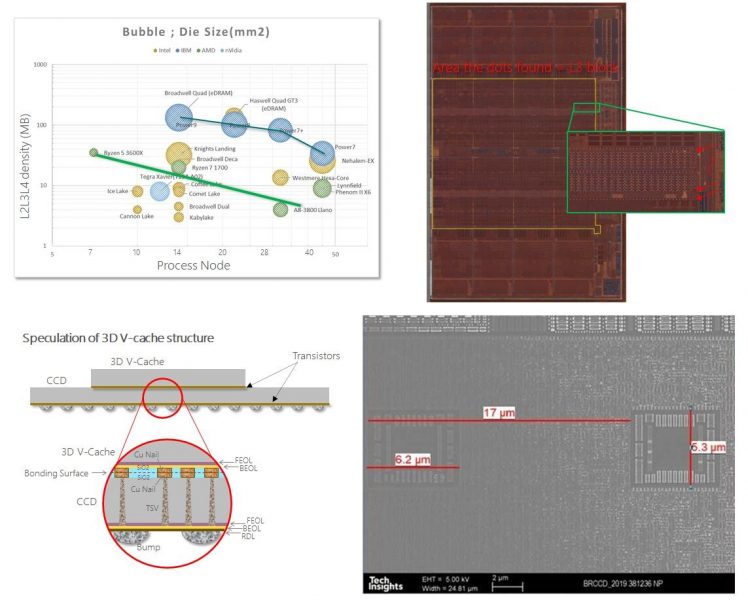

El proceso de instalación del apilamiento utiliza una tecnología denominada vías «a través del silicio», o TSV, que une la segunda capa de la SRAM al chip mediante una unión híbrida. El uso de cobre para los TSV en lugar de la soldadura habitual permite una mayor eficiencia térmica y un mayor ancho de banda. Esto sustituye al uso de soldadura para conectar los dos chips entre sí.

Fukuzaki estima que aproximadamente 23.000 TSV (vías a través del silicio), cada una de aproximadamente 17 µm de tamaño, conectan la matriz 3DV Cache al CCD principal.

«Para hacer frente al problema de #memory_wall, el diseño de la memoria caché es importante. Por favor, tome el gráfico en la imagen adjunta, la tendencia de la densidad de caché sobre los nodos de proceso. En el mejor momento por razones económicas, la integración de la memoria 3D en la lógica puede contribuir a tener un mayor rendimiento. Los chips #IBM #Power tienen una gran cantidad de caché y una fuerte tendencia. Pueden hacerlo gracias a la CPU de servidor de gama alta. Con la integración de CPUs #Chiplet iniciada por AMD, pueden utilizar el #KGD (Known Good Die) para deshacerse de la preocupación por el bajo rendimiento de las matrices monolíticas a gran escala. Esta innovación se espera para 2022 en #IRDS (International Roadmap Devices and Systems) Más Moore y AMD lo harán.»