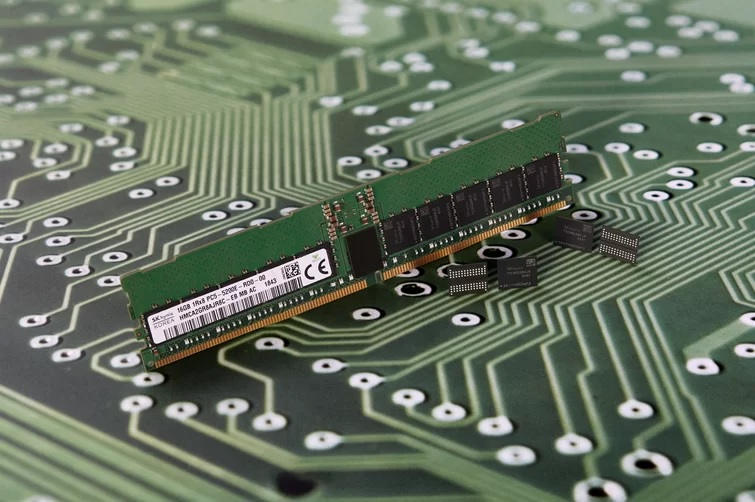

SK Hynix está empezando a mostrar detalles de su primer chip DDR5. El nuevo estándar de memorias está bajo desarrollo por parte de Jedec, pero parece que ya está saliendo a la luz.

DDR5 (Double Data Rate 5) todavía está en desarrollo por la organización Jedec, y ofrece el doble de ancho de banda y el doble de densidad que DDR4, además de mejor eficiencia. El estándar se esperaba terminado para el año pasado, pero todavía sigue en progreso. Los productos DDR5 ahora se esperan que empiecen a verse para fines de este año.

Dongkyun Kim, un diseñador de chips de Hynix, presentó el chip Hynix DDR5 el Miércoles en la ISSCC, un chip SDRAM de 16Gb de 6.4 Gb/s por pin, que corre a 1,1V y mide 76,22 mm². El dispositivo fue fabricado con un proceso DRAM 1y-nm de 4 metales.

Kim describió la implementación de un loop de delay bloqueado (DLL) modificado, usando un rotador de fase y un oscilador de inyección bloqueada para reducir el cambio de clock y la distorsión del ciclo de trabajo del clock, asociado con el uso de clocks altos. También describió otras técnicas usadas por el equipo de diseño de Hynix, incluyendo un método de entrenamiento de nivel de escritura para desfasar los problemas de clock asociados con altas velocidades y un circuito de ecualización de feedback hacia adelante (FFE) modificado.

Samsung, mientras tanto, presentó un SDRAM LPDDR5 de 10nm capaz de transmitir 7.5Gb/s a 1,05V.

Jedec anunció a principios de semana la publicación del estándar LPDDR5, que eventualmente operará con un ratio de E/S de 6400 MT/s. Se espera que también se mejore la velocidad de memoria y la eficiencia para aplicaciones como smartphones, tablets y notebooks ultra delgadas.

¿Qué opinan de estas nuevas memorias DDR5?

Fuente: Guru3D