El fabricante chino de chips Biren Technology planea tener lista (finalizar el diseño) su primera GPU de 7 nm en el tercer trimestre de este año, con un lanzamiento oficial previsto para 2022. Según el CTO de la compañía, Mike Hong, la GPU se diseñará para entrenar redes neuronales y machine learning, y se enfrentará a la GPU Tensor de próxima generación de NVIDIA (basada en la microarquitectura Ada Lovelace). Si bien es probable que esta ultima sea la mejor opción, sigue siendo bastante increíble, que una empresa China compita directamente con NVIDIA.

Biren Technology competirá contra NVIDIA

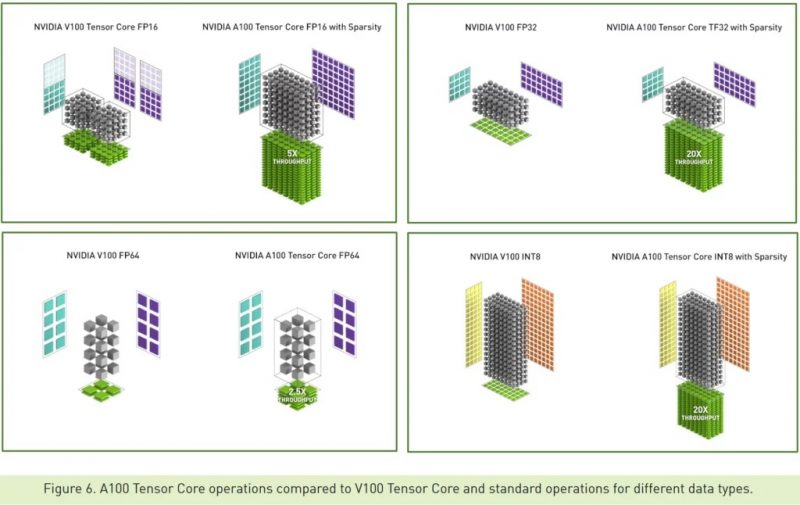

Al igual que las GPU Tesla de NVIDIA y la nueva A100, la GPU de Biren está dirigida a centros de datos que requieren soporte para cómputo de baja precisión como FP16, INT16 e INT8. Como tal, no será capaz de renderizar gráficos como las GPU convencionales y la canalización de gráficos será reemplazada por una estructura orientada a la computación.

La compañía busca aprovechar las unidades de procesamiento de flujo de datos y caché avanzada con paquetes de memoria 3D (memoria HBM integrada) en lugar de solo procesadores vectoriales que son la base de las GPU tradicionales. El primero parece parecerse a las DPU de NVIDIA, que son una adición relativamente nueva al espacio del centro de datos y deberían permitir que la GPU sea más flexible en términos de sus capacidades de procesamiento de datos.

Una unidad de procesamiento de datos (DPU) es un circuito electrónico especializado y programable con aceleración por hardware del procesamiento de datos para la computación centrada en datos. Los datos se transmiten hacia y desde el componente como paquetes de información multiplexados. Una DPU generalmente contiene una CPU, NIC y motores de aceleración de datos programables. Esto permite que las DPU tengan la generalidad y la capacidad de programación de las unidades centrales de procesamiento, al mismo tiempo que se especializan para operar de manera eficiente en paquetes de red, solicitudes de almacenamiento o solicitudes de análisis.

El motor de aceleración de datos se diferencia de una CPU por un mayor grado de paralelismo (requerido para procesar muchas solicitudes) y de una GPU por una arquitectura MIMD en lugar de una arquitectura SIMD (requerido ya que cada solicitud necesita tomar decisiones diferentes y seguir un camino diferente a través de el chip). Las DPU pueden estar basadas en ASIC, FPGA o SoC. Las DPU se han utilizado cada vez más en centros de datos y supercomputadoras desde su introducción en la década de 2010 debido al aumento de la computación centrada en datos, big data e inteligencia artificial/machine learning/deep learning.